#### GENI CRKit Spiral 2 Year-end Project Review

# <University of Colorado, Boulder, Rutgers University, RTS > PI: Dirk Grunwald Co-PI: Peter Wolniansky, Ivan Seskar Staff: Prasanthi Maddala, Khanh Le

August 25th, 2010

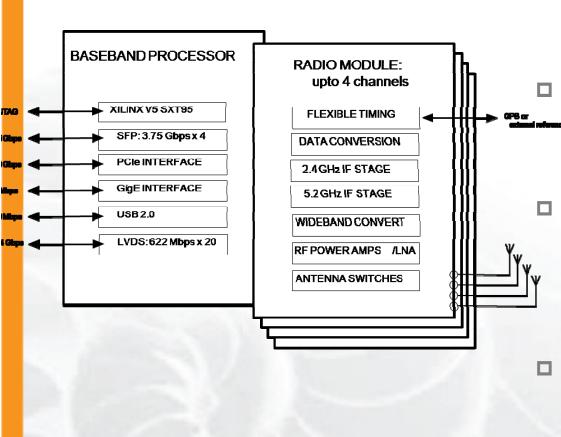

# **CRKit**

#### **Open Source Platform**

- Range of COTS baseband FPGA platforms

- □ Medium size (LX50)

- □ Large size (SX95)

- □ Standard interfaces:

- □ 1000 BaseT, (SFP)

- □ USB

- □ (8x PCIExpress)

- 4 (2) configurable radio modules for phased or smart antenna applications:

- □ SDR/F 25 MHz, 100 M -2.4/5GHz

- □ WDR 25 MHz, 100MHz -7.5GHz

- □ XDR 500 MHz, 100MHz-7.5GHz

- Application framework with support for both RTL and Matlab (Simulink)

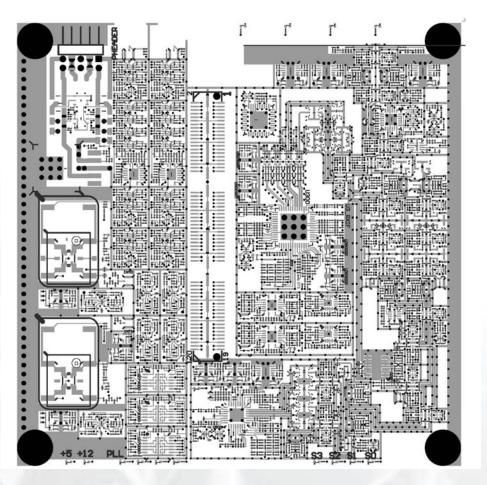

# WDR RF Front-end (Curr: WDR v2.02)

- 14 layer PCB with high-frequency 5.5 mil thick NELCO N4000-13 material

- 6000 part footprints with more than 4800 parts

- One to four independent radio modules on one (FPGA) processor.

- Each module allows two up to 40 MHz bands from 100 to 7500 MHz

- 12 bit ADC sampling up to 80MSps on both I and Q rails.

- NF = 6dB, optional external LNA for customized applications.

- 70dB of RX gain control.

- 14 bit DAC sampling upto 200MSps on both I and Q rails.

- +20dBm TX output power with fast gain control.

- 60 dB of TX gain control

- Supports full duplex operation.

- 1 usec RF frequency switching time

- Switched antenna diversity for both TX and RX channels

- Comprehensive reference clock selection or generation with internal, external or digitally derived sample clocks.

- Extensive built-in-test for monitoring system status and health (including loopback).

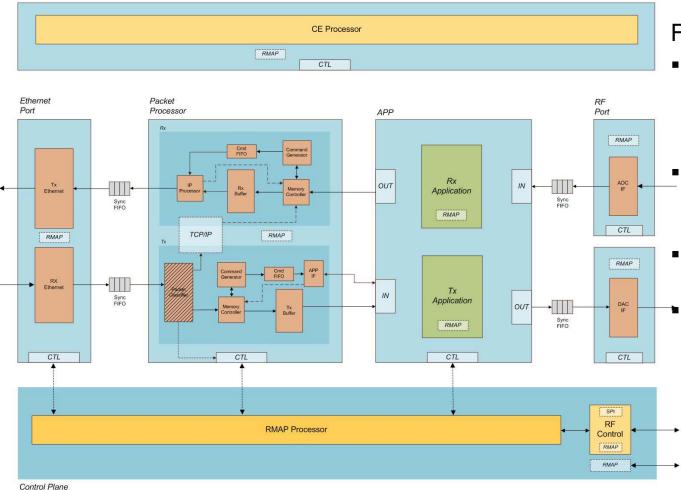

## **CRKit Framework**

#### Timing Control

#### Feature :

Board IO

- Fully functional FPGA development platform with Pluggable User Apps.

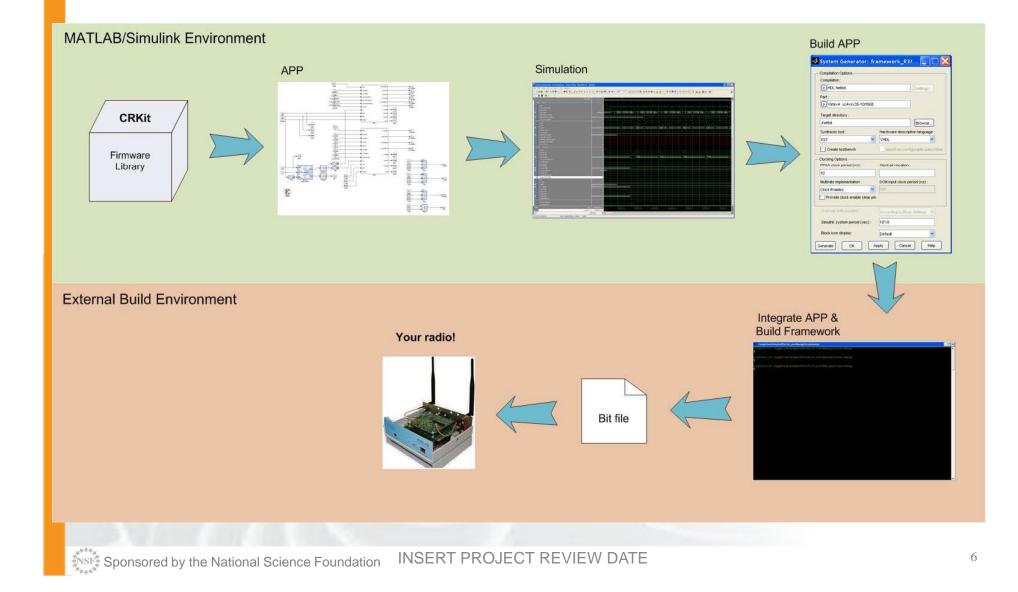

- Two environments: MATLAB/Simulink or VHDL/Verilog/BlueSpec

- Communication with Host using GbE links

- Streamlined FPGA building process e.g. HW design made-easy using MATLAB/Simulink and build scripts.

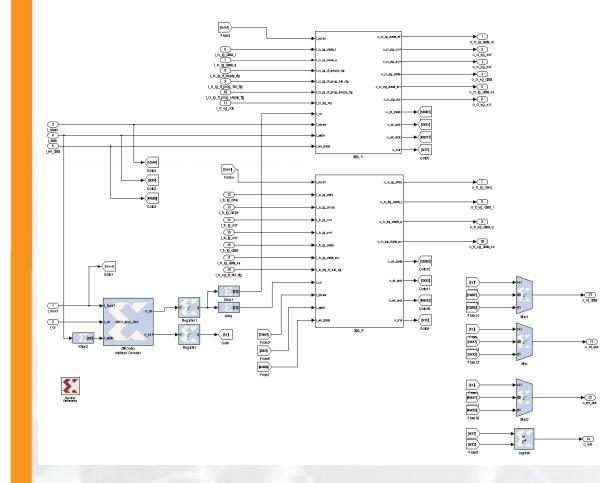

# **APP Development**

APP subsystem:

- Build App as separate entity in MATLAB/Simulink, then integrate into Framework.

- Integration of Tx and Rx subsystems

- Well-defined IO interfaces between APP and Framework.

- Either develop own Tx/Rx Apps, or select from libraries

### **Framework Design Flow**

# **Milestone & QSR Status**

| ID  | Milestone                                                    | Status                                                                                                                                                        | On<br>Time? | On<br>Wiki? | GPO<br>signoff? |

|-----|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----------------|

| S2a | Roadmap for stand-alone and<br>infrastructure-class platform | Roadmap was released at GEC7                                                                                                                                  | Late        | Yes         | Yes             |

| S2b | Phase 1 radio card for stand-alone system                    | The first prototype with extended RF<br>range was demonstrated at GEC7. Full<br>version of WDR RF stage will be<br>delivered in time for GEC9                 | Late        | Yes         | Yes             |

| S2c | Integrate stand-alone platform                               | Stand-alone platform was demonstrated at both GEC7 and GEC8                                                                                                   | Late (?)    | Yes         | No              |

| S2d | Initial integration stand-alone system and with OMF          | Initial integration with OMF was demonstrated at GEC8                                                                                                         | Yes         | No          | No              |

| S2e | Stand-alone system available to GENI users                   | Two nodes are available for remote<br>access as part of ORBIT <sup>*</sup> . The platform is<br>also available for purchase from Radio<br>Technology Systems. | Early       | No          | No              |

| S2f | Release design information for stand-<br>alone system kit    | Framework as well as all of the technical information is continuously released at http://crkit.orbit-lab.org                                                  | Early       | No          | No              |

| S2g | Contribution to GENI outreach                                | Two undergraduate students were<br>involved in framework testing and<br>verifications as part of the WINLAB<br>Summer Internship                              |             | No          | No              |

\*Note: issues with Xilinx and Matlab licenses for general public use

### Accomplishments 1: Advancing GENI Spiral 2 Goals

Deep Programmability:

CR-GENI kit (both platform and framework) are designed with focus on versatility (in both RF flexibility and baseband capabilities of the FPGA platform).

Slicing:

• The demo @ GEC8 illustrated simultaneous and independent scanning and communication. Slicing capabilities are limited by FPGA resources

#### Rapid experimentation:

• The platform can be readily used for quick development of various wireless experiments and demos.

### Accomplishments 2: Other Project Accomplishments

- On parallel funding at Colorado, transmitter chain as been improved

- Support for NC-OFDM waveform

- Support for "blind synchronization" across NC-OFDM waveform

- Support for Hierarchical Coding

- Support for enhanced modulation rates

- Papers at ANCS, CoroNet WinHEC

- Started development of Bluespec conversion of pipeline

- Stalled because undergrad (supported by NSF) at LLNL for summer

#### Issues

- Main issue to date is the use of licensed software (namely Xilinx and Matlab) that is required for FPGA code development. This is especially troublesome for deployments in remotely accessible testbeds not only because it requires that each user have a valid license, but because most academic licenses require that the actual development be done on the machines that belong to the licensee (rather than on the infrastructure machines that the testbed provides). Same issue exists for other FPGA based solutions (like NetFPGA)

- Specification tools like BlueSpec reduce some of these issues (matlab/simulink), but don't get around basic Xilinx license issue

- Outreach to Xilinx Research at Colorado to explore options

- What are you plans for the remainder of Spiral 2?

- Conversion of waveform to more modular form (BlueSpec)

- Validation of waveform control across wide-band front-end

- Further development of basic communication blocks (GENI Radio Library)

- Phase 2 radio development (wider baseband)

- Multi-FPGA support and design partitioning

- The GPO is starting to formulate goals for Spiral 3. What are your thoughts regarding potential Spiral 3 work?

- Wider GENI deployment